1

GATE CSE 2004

MCQ (Single Correct Answer)

+2

-0.6

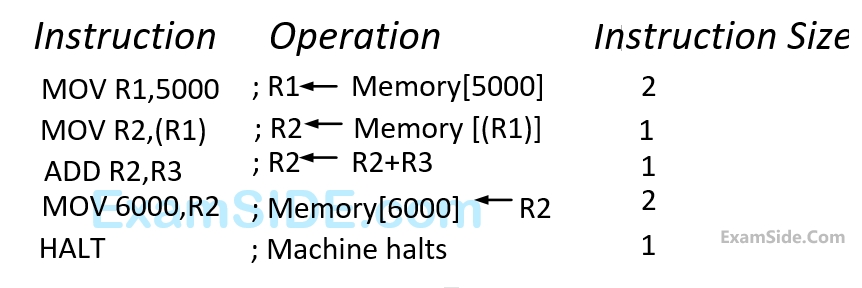

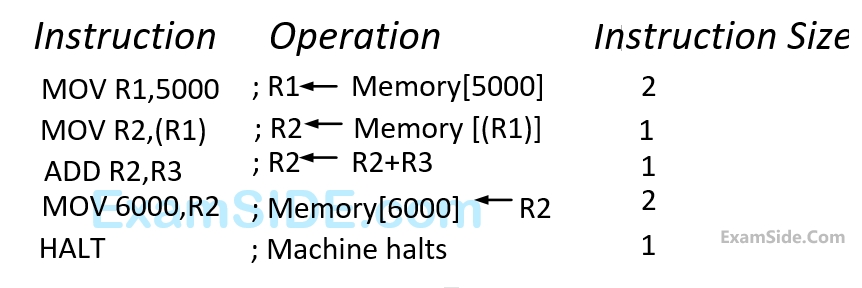

Consider the following program segment for a hypothetical $$CPU$$ having three user registers $$R1,R2, $$ and $$R3.$$

Let the clock cycles required for various operations be as follows:

Register to/from memory transfer:

$$3$$ clock cycles

ADD with both operands in register:

$$1$$ clock cycle

Instruction fetch and decode:

$$2$$ clock cycles per word

The total number of clock cycle required to execute the program is

2

GATE CSE 2001

MCQ (Single Correct Answer)

+2

-0.6

Which is the most appropriate match for the items in the first column with the items in the second column?

$$X.$$ Indirect Addressing

$$Y.$$ Indexed Addressing

$$Z.$$ Base Register Addressing

$${\rm I}.\,\,$$Array implementation

$${\rm II}.\,\,$$Writing relocatable code

$${\rm III}.\,\,$$Passing array as parameter

$$X.$$ Indirect Addressing

$$Y.$$ Indexed Addressing

$$Z.$$ Base Register Addressing

$${\rm I}.\,\,$$Array implementation

$${\rm II}.\,\,$$Writing relocatable code

$${\rm III}.\,\,$$Passing array as parameter

Questions Asked from Marks 2

GATE CSE 2025 Set 1 (1) GATE CSE 2024 Set 2 (2) GATE CSE 2023 (1) GATE CSE 2021 Set 2 (1) GATE CSE 2020 (1) GATE CSE 2018 (1) GATE CSE 2016 Set 2 (1) GATE CSE 2015 Set 3 (1) GATE CSE 2015 Set 2 (1) GATE CSE 2014 Set 1 (2) GATE CSE 2013 (1) GATE CSE 2011 (1) GATE CSE 2008 (3) GATE CSE 2006 (3) GATE CSE 2005 (1) GATE CSE 2004 (2) GATE CSE 2001 (1)

GATE CSE Subjects

Theory of Computation

Operating Systems

Algorithms

Digital Logic

Database Management System

Data Structures

Computer Networks

Software Engineering

Compiler Design

Web Technologies

General Aptitude

Discrete Mathematics

Programming Languages

Computer Organization