A positive-edge-triggered sequential circuit is shown below. There are no timing violations in the circuit. Input $P 0$ is set to logic ' 0 ' and $P 1$ is set to logic ' 1 ' at all times. The timing diagram of the inputs SEL and $S$ are also shown below.

The sequence of output $Y$ from time $T_0$ to $T_3$ is $\qquad$ .

In the circuit shown below, the AND gate has a propagation delay of 1 ns . The edgetriggered flip-flops have a set-up time of 2 ns , a hold-time of 0 ns , and a clock-to-Q delay of 2 ns .

The maximum clock frequency (in MHz , rounded off to the nearest integer) such that there are no setup violations is___________ .

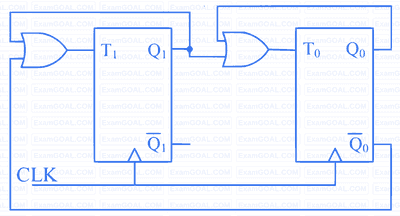

The sequence of states $(Q_1 Q_0)$ of the given synchronous sequential circuit is ________.

In a given sequential circuit, initial states are Q$$_1$$ = 1 and Q$$_2$$ = 0. For a clock frequency of 1 MHz, the frequency of signal Q$$_2$$ in kHz, is ___________ (rounded off to the nearest integer).