The signal-to-noise ratio (SNR) of an ADC with a full-scale sinusoidal input is given to be 61.96 dB. The resolution of the ADC is __________ bits (rounded off to the nearest integer).

List 1

A. Flash converter

B. Dual slope converter

C. Successive approximation Converter List 2

1. requires a conversion time of the order of a few seconds

2. requires a digital- to- analog converter

3. minimizes the effect of power supply interference.

4. requires a very complex hardware.

5. It is a tracking A/D converter.

List - 1

A. Successive approximation

B. Dual-slope

C. Parallel Comparator

List - 2

1) 1

2) 8

3) 16

4) 256

5) 512

A full scale sinusoidal signal is applied to a 10-bit ADC. The fundamental signal component in the ADC output has a normalized power of 1 W, and the total noise and distortion normalized power is 10 $\mu$W. The effective number of bits (rounded off to the nearest integer) of the ADC is _______.

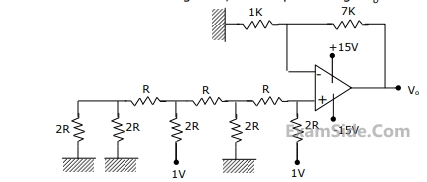

Consider the circuit shown with an ideal OPAMP. The output voltage V0 is __________ V (rounded off to two decimal places).

If the flash ADC has 8 bit resolution, which one of the following alternatives is closest to the maximum sampling rate?

If the flash ADC has 8 bit resolution, which one of the following alternatives is closest to the maximum sampling rate?The counter starts from the clear state.

The magnitude of the error between VDAC and Vin at steady state in volts is

The counter starts from the clear state.

The stable reading of the LED display is

$${V_{R\,}}\, = \,10V$$ and $$R\, = \,10k\Omega $$

The current i is

$${V_{R\,}}\, = \,10V$$ and $$R\, = \,10k\Omega $$

The voltage V0 is

In the figure shown above, the ground has been shown by the symbol $$\nabla $$

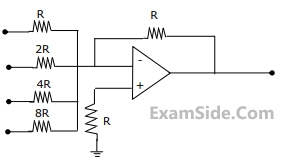

The input bits 0 and 1 are represented by 0 and 5 V respectively. The OP- AMP is ideal, but all the resistances and the 5V inputs have a tolerance of ±10%.

The input bits 0 and 1 are represented by 0 and 5 V respectively. The OP- AMP is ideal, but all the resistances and the 5V inputs have a tolerance of ±10%.

The specification (rounded to the nearest multiple of 5%) for the tolerance of the DAC is